|

|

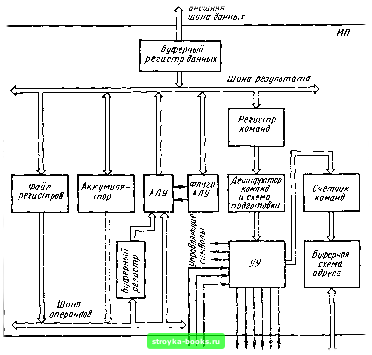

Главная Микропроцессорные системы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [ 26 ] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] типы микропроцессорных структур можно разделить на следующие категории: однокристальные МП, содержащие в одной БИС как обрабатывающую, так и управляющую части и многокристальные МП, в которых устройство управления, как правило, выполнено в виде отдельной БИС, а обрабатывающая часть может иметь многокристальную структуру. В однокристальных микропроцессорах функциональная законченность и автономность достигается использованием следующих основных архитектурных решений: применением блоков РОН, использованием стэка, параллельной обработкой кодов адреса и данных, использованием команд с различными видами адресации, асинхронным принципом выполнения операций, при котором время их выполнения зависит от вида операции. Упрощенный вариант функциональной схемы однокристального МП с двухшинной организацией приведен на рис. 3.9. Функциональная схема однокристального МП с одношинной организацией будет рассмотрена ниже на примере МП серии К580. Следует подчеркнуть, что для однокристальных МП характерны фиксированный набор команд и фиксированная разрядность. Произвольную разрядность в микро-ЭВМ можно обеспечить, используя многокристальные микропроцессоры, в которых обрабатывающая часть, выполненная на отдельных кристаллах, может наращиваться до требуемой разрядности. Обычно разрядность обрабатывающей части на одном кристалле - 2-4. Устройство управления в этом случае выполняется в; виде отдельной БИС и строится, как правило, на основе микропрограммного управления. В архитектуре многокристальных МП имеется ряд особенностей, связанных с возможностью их наращивания. К числу основных из этих особенностей относятся: использование трех шин данных, включение в каждую секцию МП отдельного регистра адреса памяти, связанного с внешней шиной адреса, наличие связей между соседними секциями с целью-получения сигналов переноса и заема, сигналов сдвига,  Внешние Сигналы управляющие состояния сигналы МП Внешняя шина адреса Рис. 3.9. Функциональная схема МП с двухшинной организацией необходимых при выполнении арифметических операций в АЛУ с числами большой разрядности, использование в каждой обрабатывающей секции отдельного дешифратора микрокоманд. Упрощенная схема обрабатывающей секции многокристального МП приведена на рис. 3.10. Она включает 2-4-разрядное АЛУ, имеющее дополнительные внешние входы и выходы сигналов переноса и сдвига, файл регистров, используемых в качестве сверхоперативной памяти или для других целей, например для организации стэка, аккумулятор и упоминавшиеся выше регистр адреса памяти и регистр данных. Данные с внешних шин и внутренних регистров, а также из аккумулятора 82 поступают на вход АЛУ через два внутренних мультиплексора. Мультиплексор представляет собой устройство, обеспечивающее поочередное подключение к одной общей шине нескольких шин данных. Функцию мультиплексора в этом случае может выполнять, например, схема, изображенная на рис. 3.7. Использование внутрен- Сигна/1 сдвига Шина адреса памяти

Сигнал переноса 1 6 следующую секцию УправптщаесияВт LLLLL Микрокоманды от ПЗУ микрокоманд Дешифратор > микрокоманд Мультиплексор "1 Шина результата С Регистр дамныи Файл регистров Мультиплексор Шина, данных А Сигнал еЗвига Сигнал переноса из предыдущей секции Шина данных в Рис. 3.10. Функциональная cxeivra обрабатывающей секции многокристального МП них мультиплексоров уменьшает площадь, занимаемую внутренними шинами на кристаллах. На основе использования секций многокристального микропроцессора можно разработать универсальный микропрограммируемый ЦП микро-ЭВМ любой разрядности [И, 12], функциональная схема которого приведена на рис. 3.11. В его основу положено следующее архитектурное решение: трехшинная организация, использование большого числа универсальных регистров, внутренний стэк, наличие индексных регистров и микропрограммное устройство управления. ЦП должен содержать и ряд таких стандартных элементов, как буферные регистры и мультиплексор ввода - вывода. Такой универсальный ЦП обладает максимальной функциональной гибкостью, поскольку может программироваться, и максимальным быстродействием за счет использования трехшинной организации и, как правило, биполярной технологии, на основе которой выполняются 6* 83 [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [ 26 ] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] 0.0011 |