|

|

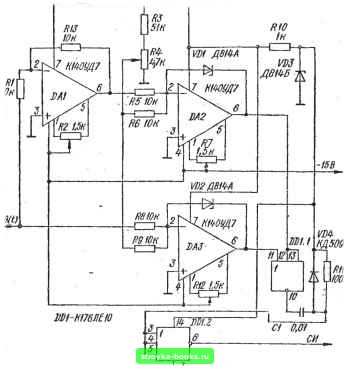

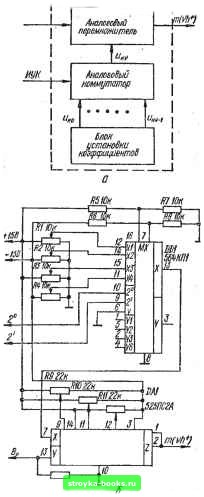

Главная Система автоматического управления [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [ 68 ] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] Инвертер Компаратор I Компаратор 2 Формирователь СИ *158  Рис. 3.5 состоит из четырех основных блоков. Первый блок - устройство выборки и хранения WBX - объединяет квантователь (мгновенный ключ) и фиксатор нулевого порядка. Проста-я схема УВХ показана на рис. 3.4. Ключ VT1 на полевом транзисторе типа КП103И размыкается и замыкается командным сигналом - импульсами управления УВХ (ИУВХ). Когда ключ замкнут, выходной сигнал УВХ изменяется в соответствии с входньш сигналом ошибки в(0. Когда ключ разомкнут, выходной сигнал определяется напряжением на конденсаторе С1, которое подается на буферный усилитель DA1 с высоким входным сопротив-  ~аО о *Ав в Рис 3.6 лением, собранный на микросхеме типа К574УД1. Поскольку время выборки (временной интервал, в течение которого ключ замкнут) значительно меньше периода Т = Nh, то сигнал на выходе VBX ©„ = в (пТ+) = е (О при / = «7"+, Т = Nh, п = = О, 1, 2, 3, ... . Второй блок - устройство синхронизации УС, которое при скачкообразном изменении входного сигнала © {() обеспечивает немедленную отработку этого изменения. Устройство синхронизации (рис. 3.5) состоит из инвертора (операционный усилитель DA1 типа КИО УД7), двух компараторов напряжения (операционные усилители DA2, DA3 типа К140УД7) и формирователя синхронизирующего импульса СИ, собранного на логических элементах DDI. 1,2 (микросхема К176ЛЕ 10). Устройство синхро- Рис. 3.7 низации имеет релейную характеристику (рис. 3.6) с регулируемой зоной нечувствительности: «ко„,, «ком2 - выходные напряжения компараторов иа операционных усилителях DA2 и DA3 при выходе сигнала в (/) за зону нечувствительности 2Д0. Величина зоны нечувствительности устанавливается переменным резистором R4 (рие. 3.5, б). Если величина сигнала в ({) превысит значение Д0, то на выходе УС сформируется синхронизирующий импульс положительной полярности амплитудой около 8 В и длительностью 100 мкс. Третий блок - устройство с переменным коэффициентом передачи К., обеспечивающее преобразование сигнала 0„ в последовательность N импульсов длительностью h, с амплитудами т (G+), m(h).....Устройство с переменным коэффициентом передачи можно реализовать с использованием усилителя с регулируемым коэффициентом передачи [43], аналогового перемножителя [2], перемножающего цифроаналогового преобразователя [2].или с использованием регулируемых делителей напряжения. На рис. 3.7 и 3.9 показаны структурные (а) и принципиальные (б) схемы двух устройств с переменньш коэффициентом передачи, обеспечивающих формирование управляющих воздействий для объектов регулирования, описываемых дифференциальными уравнениями до четвертого порядка включительно. Первое устройство (рис. 3.7, а) состоит из аналогового перемножителя напряжений (микросхема DA1 типа К525ПС2А), коммутатора аналоговых сигналов (микросхема DDI типа 564КП1) и блока установки коэффициентов передачи, выполненного в виде набора регулируемых делителей напряжения (переменные резисторы R1....R4). Постоянные напряжения Uko ••• UkN-i пропорциональные коэффициентам передачи устройства на v-m шаге в пределах интервала регулирования 7= Nh, снимаются с переменных резисторов R1....R4 и поступают на входы XI ... Х4 коммутатора аналоговых сигналов. Управление коммутатором осуществляется параллельным двоичным кодом текущего номера шага регулирования - импульсами управления коммутатором Я У/С. На выходе X коммутатора образуется последовательность импульсов и длительностью Л, амплитуды и полярности которых соответствуют требуемым коэффициентам передачи К.. Полученная последовательность импульсов поступает на вход X аналогового перемножителя напряжения, на второй вход Y которого подается сигнал G„. В результате перемножения сигналов G и «д,., на выходе Z аналогового перемножителя образуется последовательность импульсов напряжения т (vft"*"), являющаяся выходным сигналом регулятора. Эпюры, поясняющие работу рассмотренного регулятора при отработке системой на рис. 3.1 произвольного входного воздействия, изображены на рис. 3.8 (при использовании такого регулятора измерительные связи в системе отсутствуют). Второе устройство (рис. 3.9) состоит из инвертора на операционном усилителе (микросхема DA1 типа К140УД7), делителей прямого сигнала (переменные резисторы R6, R7), делителей инвертированного сигнала (переменные резисторы R4, R5) и коммутатора аналоговых сигналов MX (микросхема DDI типа К564КП1). В этом устройстве регулирующее воздействие (последовательность импульсов т (v/z")) формируется путем последовательного подключения на -интервалах времени (О, /г), (ft, 2Л), (2ft, 3ft), (3ft, 4ft) ко входу объекта регулирования напряжений "mv = вп ?«v. где Кру = К. /тах - коэффициент передачи устройства на v-m шаге регулирования; К. - расчетное значение коэффициента передачи на v-m шаге регулирования; Лща,- максимальный коэффициент передачи из числа коэффициентов К. ЭПюры, поясняющие работу Этого устройства при отработке [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [ 68 ] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] 0.0011 |