|

|

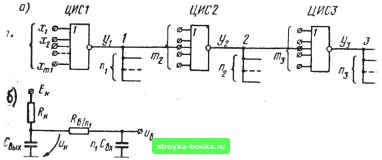

Главная Линейные элементы [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [ 52 ] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] Изменения величины Re и п мало влияют на величину /вых (так как обычно Rk>R6), но существенно влияют на величину t/вых. Если хотя бы на одном входе схемы рис. 2.44, например пер-во.м.ывх! = (т. е. Ji = 1), то Ti открыт и насыщен, напряжение на выходе Е° низкое (практически равное Ыкн); при этом транзисторы нагрузочных ЦИС заперты, так как < Uuop- Таким образом, рассматриваемая схема действительно реализует логическую функцию ИЛИ- НЕ. Мощность, потребляемая элементом в режиме включения от источника Ек. Роткр - (Ек Чк н), а в режиме выключения закр " (Ек-и ) - -р {Ек - Ыб и - hxRc)- Rk -"ихзакр/- j Если считать, что ЦИС находится половину рабочего времени в открытом состоянии, а другую половину - в запертом, то среднюю мощность, потребляемую элементом, можно определить как Rср о (/*( откр Д-Р » - If "к» г закр/ + «бн + вх/?б Переходные процессы Рассмотрим процесс переключения цифровых интегральных схем РСТЛ, соединенных последовательно (рис. 2.53а), причем i-я схема имеет /П{ входов и нагружена П{ аналогичными схемами. ВхоВод  Рис. 2.53 Пусть ЦИС 1 выключается и пусть включение ЦИС 2 начинается только после того, как коллекторный ток в ЦИС 1 спадает до нуля. В этом случае задержка включения ЦИС 2 определяется в соответствии с эквивалентной схемой (рис. 2.536) выходной цепи закрытой ЦИС 1, длительностью заряда емкости rtiCsx до порогового уровня f/nop," здесь Свх - входная емкость отпирающегося транзистора ЦИС 2, а Свых - выходная емкость, шунтирующая коллектор ЦИС 1, Если считать, что Рб/«Г< Рн [обычно /?б (0,40,6) Рн, «1 >" i>3-f-4], то можно оценить время задержки по формуле Tl = СеыхРк + П1Свх(Рк + Рб/ni). или, еще более грубо, ti = (СвыхЧ-«iCbx)Pk. Так как < Е, то "110(1 + С/ор/Е,) и в первом приближении при Uuop/Eg, < 1 Пг (2.152) Заметим, что t° растет с ростом числа нагрузок щ, числа входов fUi (от последнего зависит Свых) и с уменьшением к- Выключение ЦИС 3 начинается в момент включения ЦИС 2, так как в этот момент начинает увеличиваться коллекторный ток транзистора ЦИС 2 и, следовательно, уменьшается входной (базовый) ток транзистора ЦИС 3. Очевидно, что рассасывание избыточного заряда в базе транзистора ЦИС 3 осуществляется не постоянным током. Можно, однако, в первом приближении считать, что tl = t%-\- tp, где t% - длительность фронта включения транзистора ЦИС 2, - длительность рассасывания заряда в транзисторе ЦИС 3; обусловленная постоянным обратным током его базы hs = («бн - Икн)/(б+Рвх)-Длительность р определяется в соответствии с ф-лой (2.57), а длительность определяется ф-лой (2.56), если считать входной (базовый) ток отпирающегося транзистора ЦИС 2 постоянным и равным: Заметим, что /р растет с увеличением Re (уменьшается обратный ток базы) и с уменьшением Пч (увеличивается входной ток открытого транзистора ЦИС 3, что приводит к увеличению степени его насыщения); длительность ф увеличивается с ростом Пг и rti (уменьшается включающий ток). При прохождении через ЦИС 2 и ЦИС 3 сигнал задерживается на время tl + t\ и при идентичных схемах средняя задержка на одну ЦИС определяется как 4 ср = -Ь о • зистора и, следовательно, степени его насыщения) и уменьшается /з [см. ф-лу (2.556)]. Увеличение т приводит к некоторому росту 4ср за счет роста з- Увеличение п может привести и к росту, и к спаду 4ср в зависимости от соотношений tl и з. Температурная зависимость 4ср в основном определяется конструкцией и технологией изготовления ЦИС. Характеристики элементов РСТЛ, НСТЛ Нагрузочная способность п ограничена, как это следует из проведенного выше анализа, условием насыщения нагрузочных транзисторов Т"{Tl, Т2, ..., П). В реальных цифровых интегральных схемах НСТЛ величина п мала: пЗ. Это обусловлено в основном разбросом входных характеристик транзисторов 1б = !{иб) вследствие влияния различных технологических факторов и зависимости температуры транзисторов от их положения на поверхности монтажной платы. В результате при одинаковых напряжениях «бн на базах нагрузочных транзисторов элемента НСТЛ токи баз /вх в некоторых из них могут существенно превышать необходимый уровень насыщающего тока /бн- При этом, естественно, требуется и больший выходной ток задающего запертого элемента (на транзисторах Г); но при определенных заданных значениях Ек, Rk ток практически задан и он может быть-использован для насыщения меньшего числа нагрузочных транзисторов, чем в случае, когда все их входные характеристики идентичны. Как уже отмечалось, включение в цепи связи резисторов (схемы РСТЛ) приводит к уменьшению разброса входных токов насыщенных транзисторов, и это позволяет довести нагрузочную способность до величины п 5. Коэффициент объединения по входу {т) ограничен, так как с увеличением т растет число транзисторов Т в задающем элементе, растет суммарная выходная паразитная емкость этого элемента, что приводит к увеличению длительности фронта его выключения и, следовательно, к росту задержки включения нагрузочных элементов и к уменьшению быстродействия. Кроме того, с увеличением т растет ток, ответвляющийся в закрытые транзисторы Т\, Т2, .. ., Тт, что приводит К умсньшению входных токов открытых транзисторов нагрузочных элементов {Т", Tz, . ., Тп} вследствие чего может быть нарушено условие их насыщения. Обычно в интегральных элементах РСТЛ (НСТЛ) m 6. Быстродействие элементов НСТЛ относительно невелико, главным образом, из-за глубокого насыщения открытых транзисторов;; 4ср - обычно порядка десятков или даже сотен не. Включение резисторов Rs (схема РСТЛ) может привести к уменьшению быстродействия из-за уменьшения величин входных отпирающих и запирающих токов. Иногда для предотвращения этого резисторы Re шунтируются ускоряющими конденсаторам и [0] [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [ 52 ] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] [94] [95] [96] [97] [98] [99] [100] [101] [102] [103] [104] [105] [106] [107] [108] [109] [110] [111] [112] [113] [114] [115] [116] [117] [118] [119] [120] [121] [122] [123] [124] [125] [126] [127] [128] [129] [130] [131] [132] [133] [134] [135] [136] [137] [138] [139] [140] [141] [142] [143] [144] [145] [146] [147] [148] [149] [150] [151] [152] [153] [154] [155] [156] [157] [158] [159] [160] [161] [162] 0.0015 |