|

|

Главная Микроконтроллеры [0] [1] [2] [3] [4] [ 5 ] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] микроконтроллеры, не имеющие оперативной памяти данных (SRAM), например, AT90S1200. У этих микроконтроллеров реализован аппаратный стек глубиной 3. Это обязательно следует учитывать при написании для них программ. Все пространство памяти AVR является линейным и непрерывным. Модуль прерываний имеет собственный управляющий регистр в пространстве ввода/вывода, и флаг глобального разрешения прерываний в регистре состояния. Каждому прерыванию назначен свой вектор в начальной области памяти программ. Различные прерывания имеют приоритет в соответствии с расположением их векторов. По младшим адресам расположены векторы с большим приоритетом. Режимы адресации Прямая регистровая адресация с одним регистром Rd Данные, над которыми осуществляется операция (или используются при выполнении операции), находятся в регистре d (Rd). Прямая регистровая адресация с двумя регистрами - Rd и йг Данные, над которыми осуществляется операция, находятся в регистрах г (Rr) и d (Rd). Результат операции сохраняется в регистре d (Rd). Регастровый файл  Рис. 2.6. Прямая регистровая адресация с одним регистром Регастровый файл 15 9 54 I коп I г I Т Рис. 2.7. Прямая регисфовая адресация с двумя регистрами Прямая адресация к области ввода/вывода Память ввопа/вьюода 15j 5 О I КОП I п I Р I  Рис. 2.8. Прямая адресация к области ввода/вывода п - адрес регистра, используемого в операции, находится непосредственно в коде команды, в битах 0...5. Прямая адресация к памяти данных Память данных

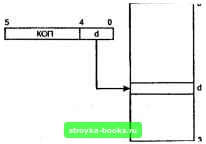

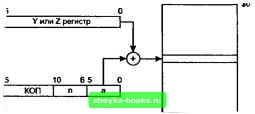

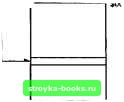

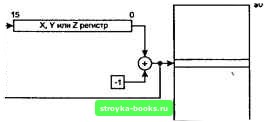

Рис. 2.9. Прямая адресация к памяти данных 16-разрядный адрес ячейки памяти данных находится в коде команды, состоящей из двух слов. Rr/Rd определяет регистр, используемый при работе с памятью данных (т. е. регистр, куда записываются результаты операции либо откуда они берутся для выполнения операции). Косвенная адресация к памяти данных со смещением Память данных  Рис. 2.10. Косвенная адресация к памяти данных со смещением Адрес операнда определяется как сумма содержимого Z или Y регистра и бит 0...5 кода команды. Косвенная адре€яция к памяти данных Память данных 15 О I X. Y или Z регистр -  Рис. 2.11. Косвенная адресация к памяти данных Адрес операнда находится в Х-, Y- или Z-регистре. Косвенная адресация к памяти данных с предварительным декрементом Память данных  Рис. 2.12. Косвенная адресация к памяти данных с предварительным декрементом [0] [1] [2] [3] [4] [ 5 ] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] [33] [34] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] [48] [49] [50] [51] [52] [53] [54] [55] [56] [57] [58] [59] [60] [61] [62] [63] [64] [65] [66] [67] [68] [69] [70] [71] [72] [73] [74] [75] [76] [77] [78] [79] [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93] 0.0011 |

||||||||||||||||||